R. R. Logic Systems

- 06 Apr, 2011 RRLogic registered as a Private Limited Company

- 12 May, 2011 RRLogic bags its first contract with Parallocity Inc.

- 19 May, 2011 RRLogic enters into contract with Saankhya Labs for GCC porting

- 07 Jun, 2011 Vayavya Labs added to the list of esteemed clients

- 04 Aug, 2011 AMD enters into general services contract with RRLogic

- 17 Oct, 2011 ANURAG Labs (DRDO) contracts RRLogic for Compiler Validation

- 15 Nov, 2011 AMD requests additional compiler resources from RRLogic

- 15 Jan, 2012 RRLogic begins development of its flagship product

- 31 Mar, 2012 Saankhya Labs compiler tool chain is delivered

- 16 Apr, 2012 AMD requisitions senior compiler engineers

- 03 Aug, 2012 AMD renews its contract with RRLogic for the second time

- 25 Aug, 2012 AMD requisitions compiler testing resources

- 30 Mar, 2013 Anurag Labs Compiler Validation project delivered

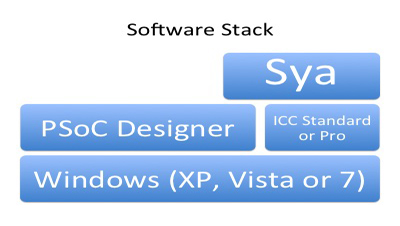

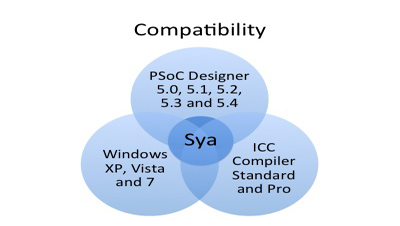

- 13 Jul, 2013 RRLogic launches its flagship product Sya for PSoC1 devices

- 04 Aug, 2013 AMD renews its contract with RRLogic

- 30 Oct, 2013 RRLogic launches its Enterprise Mobility Solutions

- 15 Nov, 2013 Tech Mahindra signs up RRLogic as preferred partner for Compiler services with DRDO

- 05 Aug, 2014 AMD renews its contract with RRLogic for the third time in a row

- 22 Sep, 2014 Cypress Semiconductor signs up RRLogic for providing engineering services

- 06 Oct, 2014 Infinite Computer Solutions signs up RRLogic as preferred partner for Compiler Services

- 27 Jan, 2015 Sandisk signs up RRLogic for providing engineering services

- 06 Apr, 2015 RRLogic completes 4 years of operations

- 06 Apr, 2015 QuickLogic signs up RRLogic for providing compiler and debugger consultancy

- 31 Aug, 2015 AMD renews its contract with RRLogic perpetually

- 24 Feb, 2016 ARM signs up RRLogic for providing engineering services

- 06 Apr, 2016 RRLogic completes 5 years of operations

- 06 Apr, 2017 RRLogic completes 6 years of operations

- 28 Jun, 2017 d'Alchemy signs up RRLogic for providing engineering services

- 04 Jul, 2017 Saankhya Labs hands out repeat order to RRLogic for supporting and extending their compiler tool chain

- 13 Jul, 2013 Sya-1.0 launched for PSoC1

- 15 Jul, 2013 Early bird offer launched for Sya-1.0

- 23 Jul, 2013 Sya-1.01 launched for PSoC1

- 25 Jul, 2017 Sya-2.0 launched

Services

R. R. Logic Systems offers services in the following areas:

Development of Back-end Optimizations

Development of Back-end OptimizationsR. R. Logic Systems is capable of developing compiler back-ends for any processor architecture using frameworks like LLVM, GCC, Open64, LCC, and SDCC. A back-end using any other proprietary framework can also be developed with a short learning curve ranging between four to ten weeks. Both architecture dependent as well as architecture independent optimizations can be developed in the back-end. The company also has experience of working with the SUIF and the SPARK frameworks.

The Company has expertise in writing multiple passes in the LLVM framework targeted at architecture specific optimizations. There are more than 12 man years of combined experience in LLVM within the team.

More recently, the team has worked on GPGPU compilers for a processor major where it has worked with both LLVM and OpenCL compiler frameworks along with an EDG front-end.

The team is familiar with using front-ends like EDG and Clang.

Porting of GCC and LLVM and Other Re-targetable Frameworks

Porting of GCC and LLVM and Other Re-targetable FrameworksThe company has extensive experience in creating clean room ports of GCC and the associated developer tools and libraries like Binutils, GDB, GLibC and uCLibC. The team in the past has carried out at least two successful ports from scratch for two RISC processors - one targeted at the Desktop systems and another targeted at the Embedded systems. A third successful port was created for a VLIW Media Processor for a subset of the C language.

Unlike most ports for such tools that use an existing port to a similar architecture as a base to create the new port, our strategy has been to write the ports from scratch, weighing the applicability of each retargetable feature to the architecture for which the port is being created. This makes sure that we do not carry forward any redundant artifacts of the base port and try to work around them in the new port. The resulting port is very clean and easily maintainable.

The team has had first hand experience in creating a clean room port of LLVM for a proprietary line of 8-bit micro-controllers and maintaining the same over a period of three years. The team is very well versed with implementing Link Time Optimizations (LTO) in LLVM.

The company has also created a prototype port of the SDCC framework for an 8-bit micro-controller.

Binary Translation, Optimization and Instrumentation

Binary Translation, Optimization and InstrumentationThe team has over 9 man years of experience in the area of binary translation, optimization and instrumentation. One of the senior members of the team has worked extensively on dynamic binary translators and instrumentation tools, notable amongst them are HP Aries and HP Caliper.

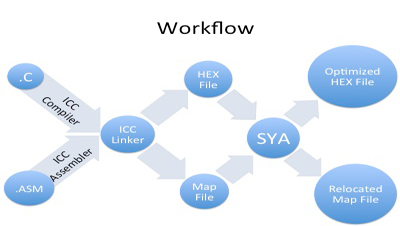

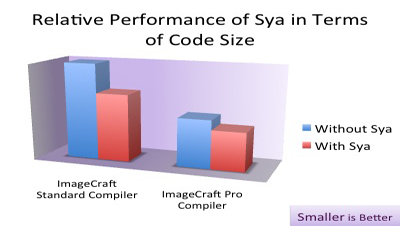

More recently, the team has developed a post link binary optimizer for an embedded systems major on a turnkey basis. The tool takes in an object file in Intel Hex format, performs optimizations on the same and generates the optimized output in another object file in the same format.

Designing Runtime Architecture (ABI)

Designing Runtime Architecture (ABI)The team is capable of designing the runtime architecture (ABI) for various linking models including but not limited to:

Dynamic Linking

Static Linking

Static Linking for Bare Metal systems

Static Linking without the C Runtime

1 x 1 Threads with or without TLS

M x N Threads with or without TLS

The team in the past has designed such ABIs for one VLIW media processor and two RISC processors - one for the workstation platform and another for the embedded platform.

PARSERS AND LINTING TOOLS

PARSERS AND LINTING TOOLSRecently the team created a lexical analyzer and a parser for a proprietary language that is used to describe devices. It generates an Abstract Syntax Tree (AST) for a tool that automatically generates device drivers from the description of the device.

The team has in the past created parsers and lexical analyzers for various languages like C, Java and VHDL. The output of such tools have been an AST. It is possible to create similar parsers for other standard or custom languages so long as the language specification in BNR or any other standard representation is made available.

The team has also created linting tools to identify and flag special constructs at the input stage of tools that do not handle such constructs. Some such typical constructs flagged by those tools include loops with pointer operations, loops with switch cases and loops with conditional execution. Identifying any other construct is also possible.

PERFORMANCE ANALYSIS OF BENCHMARKS

PERFORMANCE ANALYSIS OF BENCHMARKSThe team at R. R. Logic Systems can analyze the performance bottlenecks for benchmarks like SPECINT and SPECFP for a given compiler tool chain. The team can suggest possible optimizations in the compiler to overcome these bottlenecks. A customer specific benchmark can also be worked upon.

More recently the team worked on analysis of SPEC benchmarks for the Open64 compiler for a processor major.

The team can also customize these benchmarks to run under custom environments like without an Operating System and/or without a file system and mimic such behaviour as closely as possible so as not to perturb the essence of the benchmark.

CUSTOM LIBRARIES

CUSTOM LIBRARIESR. R. Logic Systems can develop custom libraries for specialized development platforms. The following is a possible list of libraries that can be developed:

Fixed Point Math libraries

Fixed Point Graphics libraries

C/C++ libraries without OS support

Floating Point Math libraries for Fixed Point systems

The above is not an exhaustive list of libraries that can be developed. Once the customer requirements are known, a detailed technical proposal can be given.

MAINTENANCE

MAINTENANCER. R. Logic Systems can maintain and provide regular upgrades for developer tool chains. It can perform both feature upgrades as well as defect fixes to the existing code base. A mutually agreed service level agreement (SLA) on the turnaround time for defect fixes can be adhered to. A defect tracking system that is transparent to the client can be maintained and the status of the same can be reviewed on a daily / weekly basis over a teleconference.

The types of compilers and other developer tools that can be supported are covered by the earlier items on this page.

TESTING

TESTINGThe company has experience in setting up test benches to regress compilers and other developer tools. There is reasonable expertise to develop test suites to cater to specific needs of the tool. Once these needs are listed out by the client, a detailed proposal can be given on the test plan. The team can also setup test benches using customer's own test suite and provide QA reports for the tool releases made by the client.

CERTIFICATION

CERTIFICATIONR. R. Logic Systems can certify compilers and other developer tools using standard test suites like Perennial, PlumHall, GCC Torture Suite and the like. It can provide a conformance report for such test suites and also fix defects in the tool chain to increase its compliance.